leekc_84

Junior Member level 3

Hi,

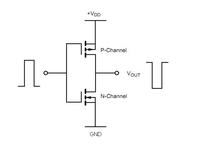

I am thinking to do a very simple high side p-mosfet power switch. Let say Vcc 5V to source, gate voltage controlled by FPGA output, and the load current is about 0.5A at the the drain, parallel with filtering capacitor.

What specific precautions will need to take care? How to determine MOSFET parameters in order to get fast turn on/off time?

Thanks for help.

I am thinking to do a very simple high side p-mosfet power switch. Let say Vcc 5V to source, gate voltage controlled by FPGA output, and the load current is about 0.5A at the the drain, parallel with filtering capacitor.

What specific precautions will need to take care? How to determine MOSFET parameters in order to get fast turn on/off time?

Thanks for help.