dipanjan

Member level 2

hi..

i need help using the resistors and capacitance in the umc_18_cmos library.

say i am using RNPPO_MM resistance...it has two terminals the positive and negative and a third terminal....i believe that is the body.what are the layers in its layout how to connect it i can only connect + and _ terminal am in trouble with the body

on looking at its layout i assume its a poly resistance between two layers of pdiff...but i cannot understand how i need to connect the body to the terminal...

can u tell me what the layers are and how can i connect the resistor third terminal to vdd or gnd.

i am also unsure weather for an rnppo_mm resistor i shud connect third terminal to body or gnd....

i tried putting a m1-Pdiff contact over it but it didnot work...

i keep getting an error in drc "wlnotr StampFloat "

please help tell me how to connect

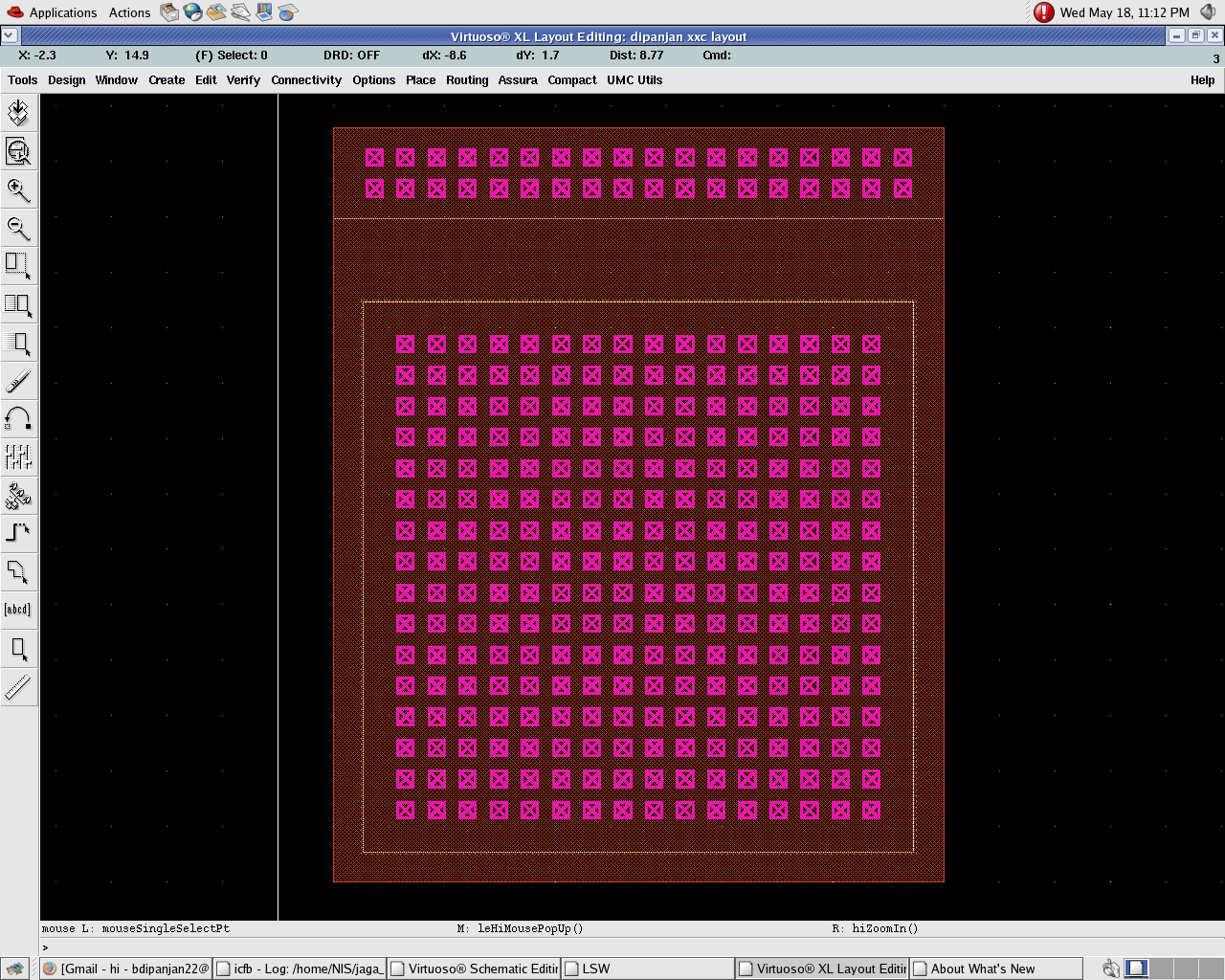

i am having similar trouble with a mimcap_mm ....it has two terminals which i can identify but what material are the contacts they appear pink in colour in layout.....can i just drag a metal wire over it and will it be connected???that will also mean i cannot roue metal wires over a cap...since the contacts are practically everyhwere....

please help i am new to using resistance and cap in layout and have no idea what to do???

please help

if u can show a screenshot of a cap (mimcap_mm) and reistance(rnppo_mm) connected between VDD and GND i will be very thankful

please in some real mess.

or show me a ckt that contains them connected in layout or a doc that might help

thank you to everyone for helping in advance

i need help using the resistors and capacitance in the umc_18_cmos library.

say i am using RNPPO_MM resistance...it has two terminals the positive and negative and a third terminal....i believe that is the body.what are the layers in its layout how to connect it i can only connect + and _ terminal am in trouble with the body

on looking at its layout i assume its a poly resistance between two layers of pdiff...but i cannot understand how i need to connect the body to the terminal...

can u tell me what the layers are and how can i connect the resistor third terminal to vdd or gnd.

i am also unsure weather for an rnppo_mm resistor i shud connect third terminal to body or gnd....

i tried putting a m1-Pdiff contact over it but it didnot work...

i keep getting an error in drc "wlnotr StampFloat "

please help tell me how to connect

i am having similar trouble with a mimcap_mm ....it has two terminals which i can identify but what material are the contacts they appear pink in colour in layout.....can i just drag a metal wire over it and will it be connected???that will also mean i cannot roue metal wires over a cap...since the contacts are practically everyhwere....

please help i am new to using resistance and cap in layout and have no idea what to do???

please help

if u can show a screenshot of a cap (mimcap_mm) and reistance(rnppo_mm) connected between VDD and GND i will be very thankful

please in some real mess.

or show me a ckt that contains them connected in layout or a doc that might help

thank you to everyone for helping in advance