blooz

Advanced Member level 2

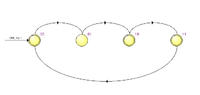

Hai the the code is as follows it compiles without error but the Waveforms when Simulated Doesnot match with Requirement .I Intended to design a mode 4 Counter but the simulation does take place but with wrong result

//Code mode 4 counter in verilog

//-----------------------------------------------------------------------------

//

// Title : No Title

// Design : verilog_systemc_parameters

// Author : Neural

// Company : Artificial_Resonance

//

//-----------------------------------------------------------------------------

//

// File : F:\My_Designs\Samples_72\verilog_systemc_parameters\compile\a1.v

// Generated : 01/23/11 13:13:12

// From : F:\My_Designs\Samples_72\verilog_systemc_parameters\src\a1.asf

// By : FSM2VHDL ver. 5.0.3.4

//

//-----------------------------------------------------------------------------

//

// Description :

//

//-----------------------------------------------------------------------------

`timescale 1ns / 1ps

module a1 (clk, out, reset);

input clk;

input reset;

output [1:0] out;

wire clk;

reg [1:0] out, next_out;

wire reset;

// BINARY ENCODED state machine: Sreg0

// State codes definitions:

`define S1 2'b00

`define S2 2'b01

`define S3 2'b10

`define S4 2'b11

reg [1:0] CurrState_Sreg0;

reg [1:0] NextState_Sreg0;

//--------------------------------------------------------------------

// Machine: Sreg0

//--------------------------------------------------------------------

//----------------------------------

// Next State Logic (combinatorial)

//----------------------------------

always @ (out or CurrState_Sreg0)

begin : Sreg0_NextState

NextState_Sreg0 <= CurrState_Sreg0;

// Set default values for outputs and signals

next_out = out;

case (CurrState_Sreg0) // synopsys parallel_case full_case

`S1:

if (clk)

begin

NextState_Sreg0 <= `S2;

next_out = 2'b01;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

`S2:

if (clk)

begin

NextState_Sreg0 <= `S3;

next_out = 2'b10;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

`S3:

if (clk)

begin

NextState_Sreg0 <= `S4;

next_out = 2'b11;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

`S4:

if (clk)

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

default:

begin

// trap state

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

endcase

end

//----------------------------------

// Current State Logic (sequential)

//----------------------------------

always @ (posedge clk or posedge reset)

begin : Sreg0_CurrentState

if (reset==1'b1)

CurrState_Sreg0 <= `S1;

else

CurrState_Sreg0 <= NextState_Sreg0;

end

//----------------------------------

// Registered outputs logic

//----------------------------------

always @ (posedge clk or posedge reset)

begin : Sreg0_RegOutput

if (reset==1'b1)

begin

out <= 2'b00;

end

else

begin

out <= next_out;

end

end

endmodule

.....

//Code mode 4 counter in verilog

//-----------------------------------------------------------------------------

//

// Title : No Title

// Design : verilog_systemc_parameters

// Author : Neural

// Company : Artificial_Resonance

//

//-----------------------------------------------------------------------------

//

// File : F:\My_Designs\Samples_72\verilog_systemc_parameters\compile\a1.v

// Generated : 01/23/11 13:13:12

// From : F:\My_Designs\Samples_72\verilog_systemc_parameters\src\a1.asf

// By : FSM2VHDL ver. 5.0.3.4

//

//-----------------------------------------------------------------------------

//

// Description :

//

//-----------------------------------------------------------------------------

`timescale 1ns / 1ps

module a1 (clk, out, reset);

input clk;

input reset;

output [1:0] out;

wire clk;

reg [1:0] out, next_out;

wire reset;

// BINARY ENCODED state machine: Sreg0

// State codes definitions:

`define S1 2'b00

`define S2 2'b01

`define S3 2'b10

`define S4 2'b11

reg [1:0] CurrState_Sreg0;

reg [1:0] NextState_Sreg0;

//--------------------------------------------------------------------

// Machine: Sreg0

//--------------------------------------------------------------------

//----------------------------------

// Next State Logic (combinatorial)

//----------------------------------

always @ (out or CurrState_Sreg0)

begin : Sreg0_NextState

NextState_Sreg0 <= CurrState_Sreg0;

// Set default values for outputs and signals

next_out = out;

case (CurrState_Sreg0) // synopsys parallel_case full_case

`S1:

if (clk)

begin

NextState_Sreg0 <= `S2;

next_out = 2'b01;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

`S2:

if (clk)

begin

NextState_Sreg0 <= `S3;

next_out = 2'b10;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

`S3:

if (clk)

begin

NextState_Sreg0 <= `S4;

next_out = 2'b11;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

`S4:

if (clk)

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

else

begin

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

default:

begin

// trap state

NextState_Sreg0 <= `S1;

next_out = 2'b00;

end

endcase

end

//----------------------------------

// Current State Logic (sequential)

//----------------------------------

always @ (posedge clk or posedge reset)

begin : Sreg0_CurrentState

if (reset==1'b1)

CurrState_Sreg0 <= `S1;

else

CurrState_Sreg0 <= NextState_Sreg0;

end

//----------------------------------

// Registered outputs logic

//----------------------------------

always @ (posedge clk or posedge reset)

begin : Sreg0_RegOutput

if (reset==1'b1)

begin

out <= 2'b00;

end

else

begin

out <= next_out;

end

end

endmodule

.....