mustangyhz

Member level 5

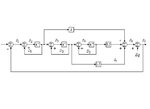

module modulator(clk, rst, k_in, v_out, v_out_offset);

input clk, rst;

input [23:0] k_in;

output [3:0] v_out, v_out_offset;

reg [3:0] v_out,v_out_offset;

reg [23:0] D1, D2, D3;

wire [23:0] sum1, sum2, sum3, sum4, sum5, sum6, sum7, v_fd, v_fd_neg;

assign sum1 = k_in + v_fd_neg;

assign sum2=sum1 + D1;

assign sum3=D1 + D2;

assign sum4=D2 + D3;

assign sum5=D2 + {D2[23],D2[23:1]};

assign sum6={D1[22:0],D1[0]} + {D3[23],D3[23:1]} +sum5;

assign sum7=sum6[23:19] + 1'b1;

always@(posedge clk or posedge rst)

begin

if(rst) D1<=24'h0;

else D1<=sum2;

end

always@(posedge clk or posedge rst)

begin

if(rst) D2<=24'h0;

else D2<=sum3;

end

always@(posedge clk or posedge rst)

begin

if(rst) D3<=24'h0;

else D3<=sum4;

end

always@(posedge clk or posedge rst)

begin

if(rst)

begin

v_out<=4'b0000;

v_out_offset<=4'b1000;

end

else

begin

v_out<=sum7[4:1];

v_out_offset<=sum7[4:1]+ 4'b1000;

end

end

assign v_fd=~sum7[4:1]+1'b1;

assign v_fd_neg={v_fd[3:0],20'h00000};

endmodule

I don't know what these code means:

assign sum7=sum6[23:19] + 1'b1;

question:4 bits for v_out, 5bits for sum7? what does "1'b1" mean?

v_out_offset<=sum7[4:1]+ 4'b1000;

what does "4'b1000" mean?

// modulator testbench

//`include "errorfeedback.v"

//'include "../../rtl/modulator.v"

module test;

reg clk;

reg rst;

reg [23:0] k_dth;

reg [31:0] bout_sum, clk_sum, averange;

wire [3:0] bout, bout1;

modulator M1(clk, rst, k_dth, bout1, bout);

always #2 clk = ~clk;

initial

begin

bout_sum = 25'b0;

clk_sum = 25'b0;

averange = 25'b0;

clk = 1'b0;

k_dth = 24'b0;

rst = 1'b1;

#100000 k_dth = 24'b000000100000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000001000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000010000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000010000000001000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000100000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b001000000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 $stop;

end

always@(posedge clk or posedge rst)

begin

if (rst)

begin

bout_sum = 25'b0;

clk_sum = 25'b0;

averange = 25'b0;

end

else

begin

bout_sum = bout_sum + bout - 8;

clk_sum = clk_sum + 1;

averange = {bout_sum,20'b0}/clk_sum;

end

end

endmodule

input clk, rst;

input [23:0] k_in;

output [3:0] v_out, v_out_offset;

reg [3:0] v_out,v_out_offset;

reg [23:0] D1, D2, D3;

wire [23:0] sum1, sum2, sum3, sum4, sum5, sum6, sum7, v_fd, v_fd_neg;

assign sum1 = k_in + v_fd_neg;

assign sum2=sum1 + D1;

assign sum3=D1 + D2;

assign sum4=D2 + D3;

assign sum5=D2 + {D2[23],D2[23:1]};

assign sum6={D1[22:0],D1[0]} + {D3[23],D3[23:1]} +sum5;

assign sum7=sum6[23:19] + 1'b1;

always@(posedge clk or posedge rst)

begin

if(rst) D1<=24'h0;

else D1<=sum2;

end

always@(posedge clk or posedge rst)

begin

if(rst) D2<=24'h0;

else D2<=sum3;

end

always@(posedge clk or posedge rst)

begin

if(rst) D3<=24'h0;

else D3<=sum4;

end

always@(posedge clk or posedge rst)

begin

if(rst)

begin

v_out<=4'b0000;

v_out_offset<=4'b1000;

end

else

begin

v_out<=sum7[4:1];

v_out_offset<=sum7[4:1]+ 4'b1000;

end

end

assign v_fd=~sum7[4:1]+1'b1;

assign v_fd_neg={v_fd[3:0],20'h00000};

endmodule

I don't know what these code means:

assign sum7=sum6[23:19] + 1'b1;

question:4 bits for v_out, 5bits for sum7? what does "1'b1" mean?

v_out_offset<=sum7[4:1]+ 4'b1000;

what does "4'b1000" mean?

// modulator testbench

//`include "errorfeedback.v"

//'include "../../rtl/modulator.v"

module test;

reg clk;

reg rst;

reg [23:0] k_dth;

reg [31:0] bout_sum, clk_sum, averange;

wire [3:0] bout, bout1;

modulator M1(clk, rst, k_dth, bout1, bout);

always #2 clk = ~clk;

initial

begin

bout_sum = 25'b0;

clk_sum = 25'b0;

averange = 25'b0;

clk = 1'b0;

k_dth = 24'b0;

rst = 1'b1;

#100000 k_dth = 24'b000000100000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000001000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000010000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000010000000001000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b000100000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 k_dth = 24'b001000000000000000000000;rst=1'b1;

#1 rst=1'b0;

#100000 $stop;

end

always@(posedge clk or posedge rst)

begin

if (rst)

begin

bout_sum = 25'b0;

clk_sum = 25'b0;

averange = 25'b0;

end

else

begin

bout_sum = bout_sum + bout - 8;

clk_sum = clk_sum + 1;

averange = {bout_sum,20'b0}/clk_sum;

end

end

endmodule

Attachments

Last edited: