lhlbluesky

Banned

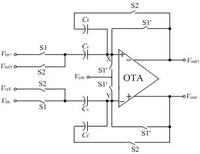

i have designed a sc circuit, as the figure shows, Cs=Cf, Vout=Vout+ - Vout- = (Vin+ - Vin-) - (Vref+ - Vref-), Vin = Vin+ - Vin- = (0V~2V), Vref = Vref+ - Vref- = 1V, Vout = Vout+ - Vout- = (-1V~+1V), my question is, when the output is small (150mV or small), the settling accuracy decreases a lot, for example: when (Vin+ - Vin-) - (Vref+ - Vref-) = 1.2V, the settling accuracy is 14bit (Vout = 1.19994V), but when (Vin+ - Vin-) - (Vref+ - Vref-) = 100mV, Vout = 99.85mV (9 bit accuracy), when (Vin+ - Vin-) - (Vref+ - Vref-) is even smaller, the settling accuracy is 8bit or less, why? what is the possible reason?

Cs=1.3pF, opamp is two stage (fold cascode + common source) with cascode compensation.

please help me, thanks all.

Cs=1.3pF, opamp is two stage (fold cascode + common source) with cascode compensation.

please help me, thanks all.