jennisjose

Member level 1

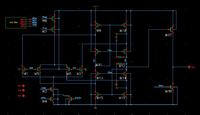

What all requirements should i meet that i can design an op-amp for 10 bit pipelined ADC? I am using switched capacitor circuits in my residue amplifier.

My VDD is 1V and am using 90 nm technology ?

I am planning to use a folded cascode op-amp without CMFB? Is CMFB important?

I am looking for a gain of 5000 and a PM of 60.

WHere can i find a step by step approach of designing such an op-amp?

My input is at 10Mhz and I plan to sample at 25 Mhz for my pipelined ADC.

What about the sample and hold circuit?

Please help

My VDD is 1V and am using 90 nm technology ?

I am planning to use a folded cascode op-amp without CMFB? Is CMFB important?

I am looking for a gain of 5000 and a PM of 60.

WHere can i find a step by step approach of designing such an op-amp?

My input is at 10Mhz and I plan to sample at 25 Mhz for my pipelined ADC.

What about the sample and hold circuit?

Please help