haribabu

Junior Member level 2

Hi ...

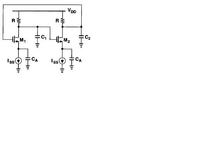

I am designing a cmos relaxation oscillator connected to a crystal . My circuit look like this ..

I connect the crystal working with resonance freq at 50MHz between the two outputs. The issue is, there are no oscillations produced at all .The circuit is getting latched .I measured the negative resistance at 50MHz which is around 5x times the oscillator resistance . Still i am not seeing any oscillations . Can anyone help me in understanding the concept and help me in designing this oscillator.

Thanks

Hari .

I am designing a cmos relaxation oscillator connected to a crystal . My circuit look like this ..

I connect the crystal working with resonance freq at 50MHz between the two outputs. The issue is, there are no oscillations produced at all .The circuit is getting latched .I measured the negative resistance at 50MHz which is around 5x times the oscillator resistance . Still i am not seeing any oscillations . Can anyone help me in understanding the concept and help me in designing this oscillator.

Thanks

Hari .