chichi

Junior Member level 3

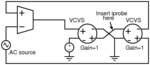

i am designing a folded cascode amplifier,with high gain and low current required,when i ever i run a monte carlo simulation in cadence while only mismatch is selected,the DM gain and CM gain vary a lot,means mismatch is really bad,can anybody tell me how to improve the mismatch of the whole circuit???thanks