cincailo

Newbie level 6

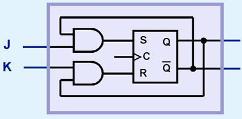

edge triggered jk flip flop

As I know that JK flip flop is to avoid the ambiguous case in SR (NAND latch) where S=R=1 is ambiguous. But I can't see from the internal circuit for JK flip flop that it can avoid ambiguous case when J=K=1. It seems it also need to depend which is start feedback Q or !Q, then only will get the toggle output. What happen when J=K=1 when initially Q=1 and !Q=0?

As I know that JK flip flop is to avoid the ambiguous case in SR (NAND latch) where S=R=1 is ambiguous. But I can't see from the internal circuit for JK flip flop that it can avoid ambiguous case when J=K=1. It seems it also need to depend which is start feedback Q or !Q, then only will get the toggle output. What happen when J=K=1 when initially Q=1 and !Q=0?