johnymo

Newbie level 1

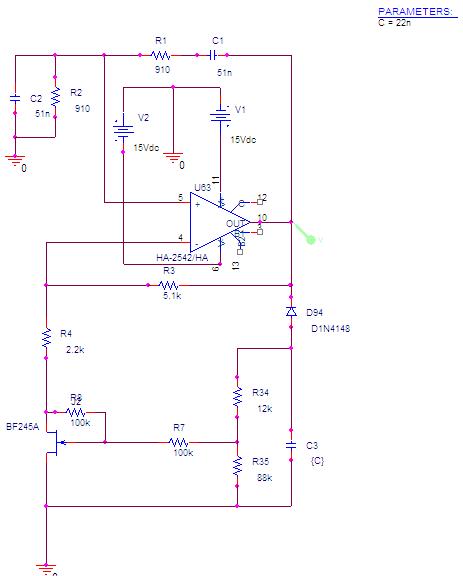

sinus generator

Hi, I have got a problem with my sinus generator based ona a Wien schematic and amplifier,that should work between 1Hz and 20kHz, I've tried everything,

I need to get Total Haramonic Disortion <1% and this is my main problem:/

This is my schematic:

I am designing it in PSpice 9.2,

please help me as You can...

I have attached this project...

best regards

Thank You

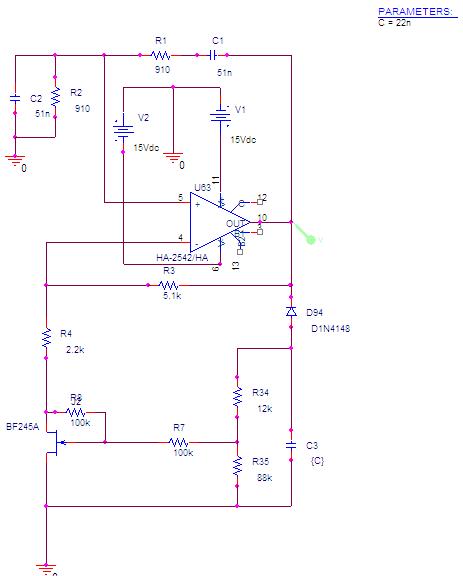

Hi, I have got a problem with my sinus generator based ona a Wien schematic and amplifier,that should work between 1Hz and 20kHz, I've tried everything,

I need to get Total Haramonic Disortion <1% and this is my main problem:/

This is my schematic:

I am designing it in PSpice 9.2,

please help me as You can...

I have attached this project...

best regards

Thank You