kingmaker

Junior Member level 2

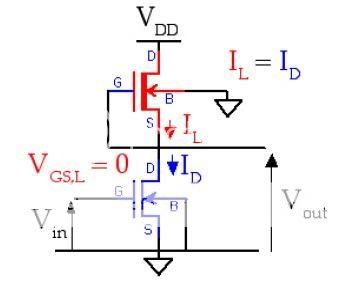

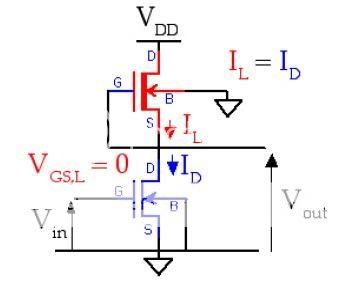

nmos inverter

For inverter circuit with depletion type nMOS load, the gate and the source nodes of the load transistor are connected, hence Vgs(load) = 0 always? why is 0 ? anyone can explain it?

For inverter circuit with depletion type nMOS load, the gate and the source nodes of the load transistor are connected, hence Vgs(load) = 0 always? why is 0 ? anyone can explain it?