naalald

Full Member level 4

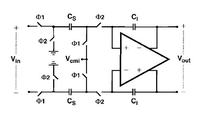

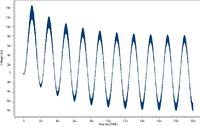

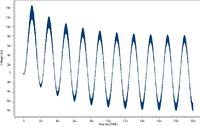

The figure below is the differential output of a switched-capacitor integrator. The input is a 1 mV sine wave: 1m×sinωt. Theoretically the output should be 16m×(1 - cosωt) but it is 16m×(0.5 - cosωt) i.e. it has a 8 mV negative offset and I don't know why? The sampling frequency is 62.5 KHz and the integrator structure is the conventional one.

What's wrong in my simulation? Any suggestions?

What's wrong in my simulation? Any suggestions?