rivendu

Junior Member level 3

hi,

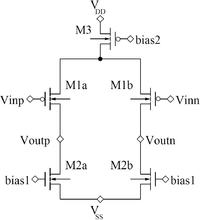

i would like to build a comparator in Output offset storage scheme like depicted below:

As the preamplifier, i want to use the differential amplifier with pmos inputs to avoid body effect.

I have a problem in dimensioning the amplifier in such a way to have it working between 0V and VDD-V_saturation. The problem is related to the grounded switches. Is it a better method to connect the switches to VDD instead of ground?

How about the setting of the bias1 and bias2 voltages. Can bias1 be set to 1 and bias2 to 0 to have maximum current flowing for higher frequencies?

thanks

i would like to build a comparator in Output offset storage scheme like depicted below:

As the preamplifier, i want to use the differential amplifier with pmos inputs to avoid body effect.

I have a problem in dimensioning the amplifier in such a way to have it working between 0V and VDD-V_saturation. The problem is related to the grounded switches. Is it a better method to connect the switches to VDD instead of ground?

How about the setting of the bias1 and bias2 voltages. Can bias1 be set to 1 and bias2 to 0 to have maximum current flowing for higher frequencies?

thanks