mohazaga

Full Member level 2

Hi ,,,

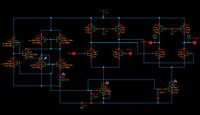

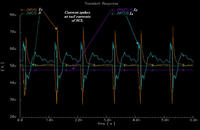

the following ckt and output signal descripe the use of beta-multiplier as current source for SCL . As input signal to SCL is a pulse 0-1 volt with 1n width ,2n period (vin2 revers vin1). The current source sinked by SCL has a spikes as clear in output waveform (I3). Why? and how to solve?

thanks

The CKT , Wn2=53*220n Ln2=2*180n

https://obrazki.elektroda.pl/44_1176386680.jpg

Output signal (currents)

https://obrazki.elektroda.pl/95_1176386865.jpg

waiting

the following ckt and output signal descripe the use of beta-multiplier as current source for SCL . As input signal to SCL is a pulse 0-1 volt with 1n width ,2n period (vin2 revers vin1). The current source sinked by SCL has a spikes as clear in output waveform (I3). Why? and how to solve?

thanks

The CKT , Wn2=53*220n Ln2=2*180n

https://obrazki.elektroda.pl/44_1176386680.jpg

Output signal (currents)

https://obrazki.elektroda.pl/95_1176386865.jpg

waiting