greprac

Newbie level 4

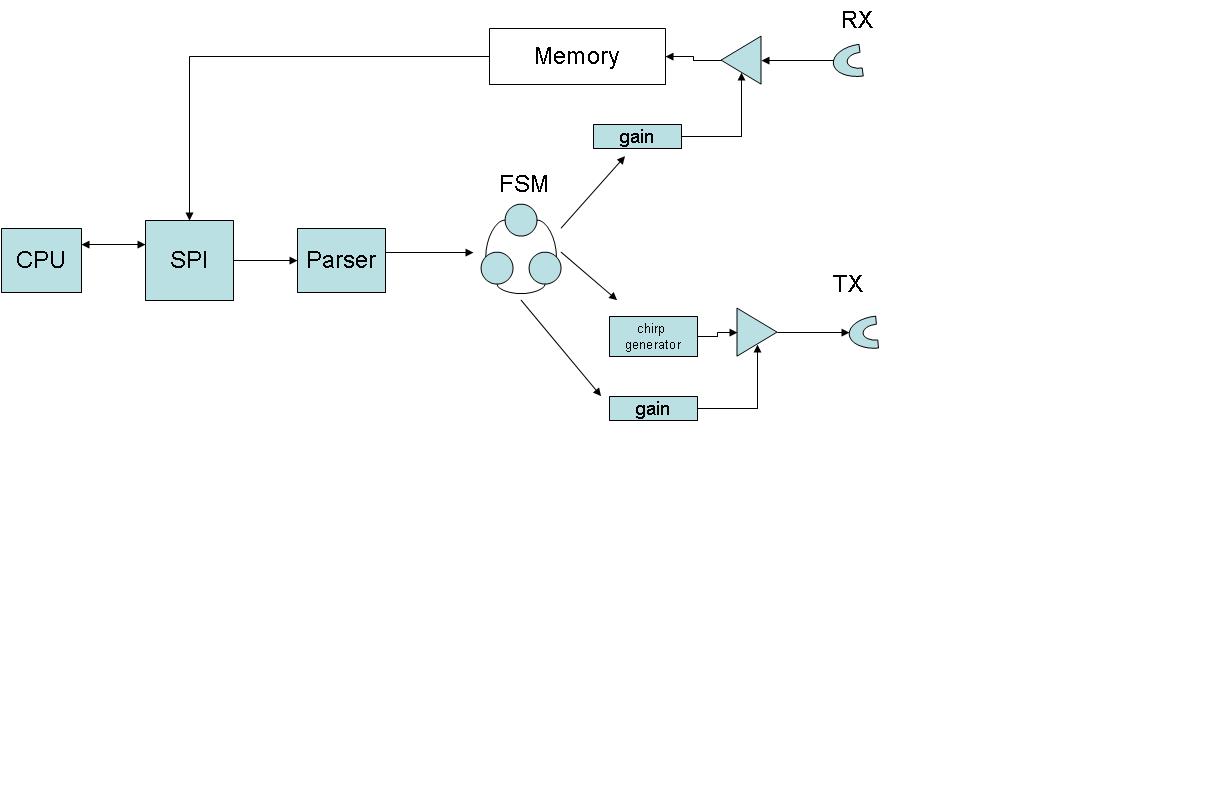

Hi frendz I need to design an Ultrasonic range finder.

Plz help as i am an amateur wid VHDL. I am uploading the diagram and for more information plz ask me. Also it doesnt have to be very complicated.

Plz help as i am an amateur wid VHDL. I am uploading the diagram and for more information plz ask me. Also it doesnt have to be very complicated.