CataM

Advanced Member level 4

- Joined

- Dec 23, 2015

- Messages

- 1,275

- Helped

- 314

- Reputation

- 628

- Reaction score

- 312

- Trophy points

- 83

- Location

- Madrid, Spain

- Activity points

- 8,409

Hello everyone,

Let's consider a situation where the bootstrap capacitor is NOT being charged during an OFF time (because the output current in e.g. a buck converter has reached 0) because the output diode is off.

The capacitor must have enough energy in order to get through that off time (without being charged) and still have energy to power the FET at the end of the idle state and to keep it ON during the on time (worst case, when the duty cycle is maximum).

After all this, the voltage of the cap must still be above the UVLO of the driver in order to not get powered off.

All this came up because I disagree with **broken link removed**.

In the paragraph right above the equation 32, TI says this (I quote):

"The bootstrap capacitor must supply all the usual discharge current components and store enough energy to be able to turn-on the switch at the end of the idle period."

However, my understanding is that one should add, at the end of TI's phrase, the italic phrase I said at the beginning and repeat here:

"and to keep it ON during the on time"

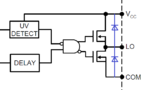

By my understanding, the equation 32 should be rewritten as in the picture below.

I am looking forward for your opinions.

Thank you for your time !

Let's consider a situation where the bootstrap capacitor is NOT being charged during an OFF time (because the output current in e.g. a buck converter has reached 0) because the output diode is off.

The capacitor must have enough energy in order to get through that off time (without being charged) and still have energy to power the FET at the end of the idle state and to keep it ON during the on time (worst case, when the duty cycle is maximum).

After all this, the voltage of the cap must still be above the UVLO of the driver in order to not get powered off.

All this came up because I disagree with **broken link removed**.

In the paragraph right above the equation 32, TI says this (I quote):

"The bootstrap capacitor must supply all the usual discharge current components and store enough energy to be able to turn-on the switch at the end of the idle period."

However, my understanding is that one should add, at the end of TI's phrase, the italic phrase I said at the beginning and repeat here:

"and to keep it ON during the on time"

By my understanding, the equation 32 should be rewritten as in the picture below.

I am looking forward for your opinions.

Thank you for your time !