mburakbaran

Member level 2

Hello all,

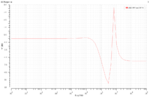

In one of my schematic level designs, for an analog amplifier, PM is supposedly 92 degrees. But when I used it in a buffer configuration, i noticed that for a square pulse, there were ringing during the slewing! I never experienced something like that. It could ring during settling and stuff, but during slewing??

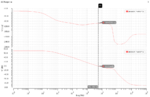

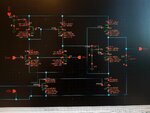

There is possibly a zero in the system, it is causing the phase go up and down for a while when the freq increased, but it never causes PM to be problematic. The gain margin is also like 12dB or sth like that.

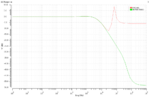

So, I connected the circuit again in buffer configuration (unity gain) and did an ac analysis. Normally you expect it to start from 0 dB, and after the GBW it should go down. But I noticed, my circuit, the gain first drops, and around 6-7 MHz it starts going up again, reaches upto 7dB, and then goes down again...

What are your thoughts?

Thanks in advance...

In one of my schematic level designs, for an analog amplifier, PM is supposedly 92 degrees. But when I used it in a buffer configuration, i noticed that for a square pulse, there were ringing during the slewing! I never experienced something like that. It could ring during settling and stuff, but during slewing??

There is possibly a zero in the system, it is causing the phase go up and down for a while when the freq increased, but it never causes PM to be problematic. The gain margin is also like 12dB or sth like that.

So, I connected the circuit again in buffer configuration (unity gain) and did an ac analysis. Normally you expect it to start from 0 dB, and after the GBW it should go down. But I noticed, my circuit, the gain first drops, and around 6-7 MHz it starts going up again, reaches upto 7dB, and then goes down again...

What are your thoughts?

Thanks in advance...