maviszeref

Newbie level 4

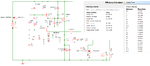

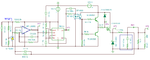

Hi. My professor wants us to design a switching regulator with an input of 9V to 32V, which will be regulated to 5V. Our circuit design is shown below. I thought that the design is a switching regulator since it has a switching waveform and an efficiency of 81 to 87% according to my simulation. I don't quite understand what he meant that it is not a switching regulator instead a linear regulator since there's no feedback. I thought lm393 provides the feedback.:thinker:

Please help me understand how can we say that it is switching or linear regulator. Thanks

Please help me understand how can we say that it is switching or linear regulator. Thanks