bio_man

Full Member level 2

Hi,

I know that I can check the transistor operating region in cadence by checking each mosfet using:

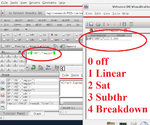

1) OP option in calculator, as shown in the attached screenshot.

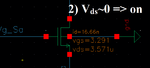

2) checking the Vds, if it is close to zero it means transistor is conducting (but can't say it is linear, sat ..etc)

However, this is tedious job, I have many transistors in the circuit I want to check them by one look. So, can anyone suggest how to show "Annotate" the transistor operating region on the schematic straightforward?

my second question about the ''Estimated operating region'' parameter in transistor: it is always showing Sat, what is the significance of this parameter? screenshot attached!

thanks in advance folks!

- - - Updated - - -

Also, kind of related question. how can I see what is the status of the transistor (sat, linear, off, ..etc) in specific interval of time? suppose I have clocks that switching some transistors on and off, I want to see how transistor changes its region of operation without make two difference simulations

I know that I can check the transistor operating region in cadence by checking each mosfet using:

1) OP option in calculator, as shown in the attached screenshot.

2) checking the Vds, if it is close to zero it means transistor is conducting (but can't say it is linear, sat ..etc)

However, this is tedious job, I have many transistors in the circuit I want to check them by one look. So, can anyone suggest how to show "Annotate" the transistor operating region on the schematic straightforward?

my second question about the ''Estimated operating region'' parameter in transistor: it is always showing Sat, what is the significance of this parameter? screenshot attached!

thanks in advance folks!

- - - Updated - - -

Also, kind of related question. how can I see what is the status of the transistor (sat, linear, off, ..etc) in specific interval of time? suppose I have clocks that switching some transistors on and off, I want to see how transistor changes its region of operation without make two difference simulations