prateekj212

Newbie level 4

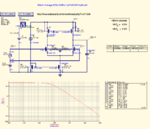

I am referring the design prcoedure from Philip Allens textbook from chapter 5.2.7. I am designing a single stage OTA with differential amplifier and current mirror load. My specifications are below:

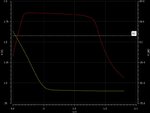

DC Gain Av = 40 dB minimum

Gain-Badnwidth = 40MHz minimum

Large signal cut off frequency 200 kHz

Output common mode typical voltage 0.9 V

Input common mode range 0.3 to 1.4 V

Supply voltage VDD 1.8V

Load capacitance 1pF

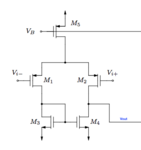

I am achieving the gain of 40 dB between 0.3 to 1.4V but my output common mode is stuck at 1.247 V which is not desired. I am using Cadence design tools. Here is the circuit below.

I am using NMOS differential pair.

Please help with proceeding with the implementation.

DC Gain Av = 40 dB minimum

Gain-Badnwidth = 40MHz minimum

Large signal cut off frequency 200 kHz

Output common mode typical voltage 0.9 V

Input common mode range 0.3 to 1.4 V

Supply voltage VDD 1.8V

Load capacitance 1pF

I am achieving the gain of 40 dB between 0.3 to 1.4V but my output common mode is stuck at 1.247 V which is not desired. I am using Cadence design tools. Here is the circuit below.

I am using NMOS differential pair.

Please help with proceeding with the implementation.