CAMALEAO

Full Member level 4

Hi everyone,

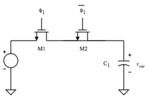

I have a question regarding mos switches. Is there any rule of thumb on designing mos switches? To things like charge injection, having the lowest resistance as possible, avoid spikes during turn on, etc?

For example, something that comes into my mind is having the pmos W 3 times the size of nmos.

Best regard.

I have a question regarding mos switches. Is there any rule of thumb on designing mos switches? To things like charge injection, having the lowest resistance as possible, avoid spikes during turn on, etc?

For example, something that comes into my mind is having the pmos W 3 times the size of nmos.

Best regard.