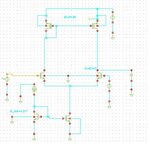

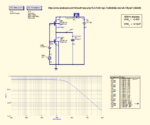

With such an extremely simple circuit (and my models)

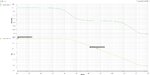

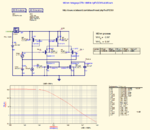

... i got 35dB gain and a UGB≈200MHz - if you don't mind the high current of 1.7mA .

... i got 35dB gain and a UGB≈200MHz - if you don't mind the high current of 1.7mA .

Note: such a circuit is just good for simulation, it's not appropriate for real analog amp design (uncontrolled drain current, high sensitivity on Vth and W/L ratio values, and PVT changes).

For higher gain and lower power consumption better use the differential amplifier version (OTA), s. my example above.

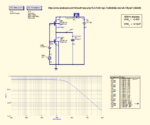

... i got 35dB gain and a UGB≈200MHz - if you don't mind the high current of 1.7mA .

... i got 35dB gain and a UGB≈200MHz - if you don't mind the high current of 1.7mA .Note: such a circuit is just good for simulation, it's not appropriate for real analog amp design (uncontrolled drain current, high sensitivity on Vth and W/L ratio values, and PVT changes).

For higher gain and lower power consumption better use the differential amplifier version (OTA), s. my example above.