niteshtripathi

Member level 3

Hi all,

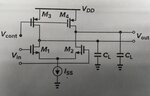

In fully differential ring oscillator , I ma using the delay cell as shown in attached image.

In this the top two mosfets will be in the triode region so that by varying the vcontrol we can vary the resistance. The MOS at the bottom, which is acting as constant current source should be in saturation across PVT.

What's about the differential input pair mosfets? It should be saturation across the PVT or what?

Hoping for any lead?

In fully differential ring oscillator , I ma using the delay cell as shown in attached image.

In this the top two mosfets will be in the triode region so that by varying the vcontrol we can vary the resistance. The MOS at the bottom, which is acting as constant current source should be in saturation across PVT.

What's about the differential input pair mosfets? It should be saturation across the PVT or what?

Hoping for any lead?