Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

The connection is mandatory by design for vertical MOSFET (all power MOSFET), and also usual for discrete small signal MOSFET (amplifiers, switches). A few discrete types with separate substrate terminal are available.

What are you talking about? PSPICE symbols? MOSFETs on the market?Shouldn't be like that.

What are you talking about? PSPICE symbols? MOSFETs on the market?

I don't exactly understand what your question is.

If you want to model MOSFETs with separate substrate, e.g. for IC design, you can do this in PSPICE. The MOSFET model has separate substrate and source terminals in any case. You preferred to use the MBreakN PSPICE symbol, which is appropriate for many technical MOSFET. If you want to model MOSFET with separate substrate, use MBreakN4.

Because most MOSFETS have the body internally tied to the one of channel connections which then makes it the source.I have seen pspice schematic transistor symbol have all its body tying to it source.

what's the reason for that?

Ok, let's talk about the regular MOS. Interchangeable? Is that mean the body is tied to it's drain?Most power MOSFETs (discrete VDMOS, integrated

LDMOS) are designed fundamentally asymmetric and

only the "regular" integrated MOSFET is commonly

symmetric (interchangeable S/D). Still the body is

fundamental to the voltage blocking and has to be

"pinned" (stiff voltage source) to ensure the D-B

blocking junction leakage does not end up going

into B-S junction (=B-E) forward biasing.

Most power MOSFETs (discrete VDMOS, integrated

LDMOS) are designed fundamentally asymmetric and

only the "regular" integrated MOSFET is commonly

symmetric (interchangeable S/D). Still the body is

fundamental to the voltage blocking and has to be

"pinned" (stiff voltage source) to ensure the D-B

blocking junction leakage does not end up going

into B-S junction (=B-E) forward biasing.

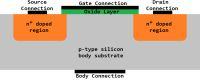

Refer the cross section view of MOSFET below,

The source and the drain terminal are 'n+ doped region' and the body is p-type substrate. Between "S" and "Body" (also "D" and Body) a diode is present, which must not be forward biased. Hence, the voltage at the "Body" terminal must not be higher than the smaller voltage of either "S" or "D" terminal.

To achieve the above mentioned condition, the "Body" terminal is either connected to lowest voltage available (usually GND/0V) or the terminal of the transistor with the lower voltage. By definition the "S" terminal is having the lower voltage. Hence, the "Body" terminal is connected to "S" terminal.

Generally, the manufacturer connects the "Body" terminal to the "S" terminal so that one of the diodes can never be forward biased and this leaves the other diode able to be forward biased.

The behaviour of MOSFET is due to body effect (back-gate effect).

The threshold voltage (Vth) of MOSFET is related

to Vsb (source-bulk voltage).

The body effect refers to the changes in the threshold voltage by the change in Vsb. Because the body influences the threshold voltage (when it is not tied to the

source), it can be thought of as a second gate (back gate). Consider the following cases,

Case 1 :

If the substrate is at 0V/GND, then you will not see body effect but if the substrate voltage is lower than 0V then the electrons will need more positive gate potential to get attracted towards the channel because the substrate potential is acting against the gate potential thus you will see the Vth of the NMOS getting increased. This is body effect. Note: It assumes source is at ground.

Case 2:

Body effect will happen, if VB is at ground and the voltage of source is increased.

Another thing, if your MOSFET is in linear operation, when the source is

connected to bulk, you don't have to deal with the "transconductance" due to Vbs (gmb), since Vbs = 0.

If you want to operate the MOSFET in linear operation, then it is better to connect the source to body (if there is separate terminal for body).so I can use option2 all the time because its more convenient? Pls note, the following 2 options generate different voltage outputs at the drain

View attachment 139954