hobbyiclearner

Full Member level 2

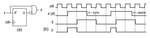

Unable to understand timing diagram of a digital ckt

Hi,

I was going through a ckt in Pedroni’s FSM book’s solution manual and was facing problems in its analysis. Hope, someone can help.

In the ckt shown in the picture, the output q of the flip flop is shown to be shifted by one clock cycle (the first rising edge of input x(d)) whereas my understanding is that output will be updated as soon as the input changes. This here is crucial as it will change the entire working of this ckt. Hence, pls. advise.

Thanks,

Hobbyicleaner

Hi,

I was going through a ckt in Pedroni’s FSM book’s solution manual and was facing problems in its analysis. Hope, someone can help.

In the ckt shown in the picture, the output q of the flip flop is shown to be shifted by one clock cycle (the first rising edge of input x(d)) whereas my understanding is that output will be updated as soon as the input changes. This here is crucial as it will change the entire working of this ckt. Hence, pls. advise.

Thanks,

Hobbyicleaner