Ata_sa16

Full Member level 6

- Joined

- Mar 29, 2016

- Messages

- 343

- Helped

- 59

- Reputation

- 118

- Reaction score

- 58

- Trophy points

- 28

- Location

- Milky Way Galaxy, 179° 56′ 39.4″

- Activity points

- 2,221

@Ata_sa16

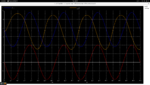

Vc is the voltage node name for V(in) of the following Gm2 circuit block.

Why does Vc drops from around 2.9V to 1.8V ?

View attachment 140634

The exact Gm2 equation as discussed in https://www.reddit.com/r/chipdesign/comments/6j8834/gyrator_implementation_of_chip_inductor/ is as follows:

View attachment 140635

I dont have any idea.

That is true. You have to write approximate equations in order to understand the circuit behavior not getting stuck in detailed small signal calculations.

in that formula if ro is high, gm4=gm3 and rd=1/gm3 (since ro3 is high), again you will reach Gm=gm1 as i wrote earlier.