Ata_sa16

Full Member level 6

- Joined

- Mar 29, 2016

- Messages

- 343

- Helped

- 59

- Reputation

- 118

- Reaction score

- 58

- Trophy points

- 28

- Location

- Milky Way Galaxy, 179° 56′ 39.4″

- Activity points

- 2,221

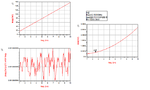

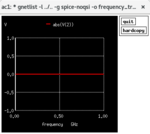

You can observe this on figures you have plotted.

Your gm is constant in green line.

I explained it several times. If you want to have constant and linear Gm for you structure you should use source degeneration.

Don't misunderstand me but I suggest you to read CMOS theory before designing these kind of circuits, it will help you a lot.

Your gm is constant in green line.

I explained it several times. If you want to have constant and linear Gm for you structure you should use source degeneration.

Don't misunderstand me but I suggest you to read CMOS theory before designing these kind of circuits, it will help you a lot.