Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

It is there so the bias to the transistor Q1 can't change rapidly. Without it, the latch circuit (Q1,Q2) could trigger on very short pulses from the comparator (stage 2), possibly even during start up when power is first applied

What isn't clear from the schematic is what the switch connected to the LED does

Does this means that when NON-INVERTING pin is left open, it has higher PD then INVERTING one ?

But I would be glad to know what value of the resistor should be placed to pull down the pin and what's the general rule for that.

input bias current will always flow directely to the Opamp.But my configuration is like this, input bias current will flow directly to the OpAmp, not through the resistor.

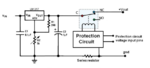

What is this V_CL and resistor circuit?

It´s not clear to me what you want to achieve