bit_an

Junior Member level 3

Hi,

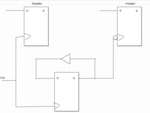

I have a chain of two flip flops, both triggered by the same clk. I want to configure the clk such that 2nd flip flop gets triggered only in the 2nd positive edge. Any delay is non-synthesizable. How to realize this in rtl design?!

Thanks

I have a chain of two flip flops, both triggered by the same clk. I want to configure the clk such that 2nd flip flop gets triggered only in the 2nd positive edge. Any delay is non-synthesizable. How to realize this in rtl design?!

Thanks