Kibos

Newbie level 4

Hello!

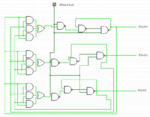

I am designing a TMR processor system. Each processor will get a clock input from a TMR clock. I finished the top level design of the system with the FPGA digital clock as reference to produce three outputs signals for each processor. I have provided synchronization through feedback, so synchronization is not a problem.

I was advised by an instructor to examine the possibility of using external crystall oscillators (hardware) and not the internal FPGA clock to prove fault masking manually by eliminating (ON/OFF) one clock at a time to manually demonstrate it.

I am using Altera DE10lite board for synthesis.

Now to the questions:

Can you use crystal oscillators to drive an FPGA processor design?

What are the risks of doing this?

Is it worth implementing it as an external module to add it (I/O pins) to the design, or just stick to the digital implementation?

Thanks!

I am designing a TMR processor system. Each processor will get a clock input from a TMR clock. I finished the top level design of the system with the FPGA digital clock as reference to produce three outputs signals for each processor. I have provided synchronization through feedback, so synchronization is not a problem.

I was advised by an instructor to examine the possibility of using external crystall oscillators (hardware) and not the internal FPGA clock to prove fault masking manually by eliminating (ON/OFF) one clock at a time to manually demonstrate it.

I am using Altera DE10lite board for synthesis.

Now to the questions:

Can you use crystal oscillators to drive an FPGA processor design?

What are the risks of doing this?

Is it worth implementing it as an external module to add it (I/O pins) to the design, or just stick to the digital implementation?

Thanks!