amir_rch

Junior Member level 3

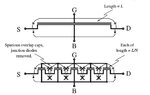

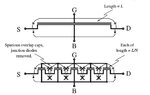

A long-channel MOS device can be viewed as a series connection of several short intrinsic MOS devices with the drains and sources of adjacent devices connected to each other. If a device of length L μm is broken into N segments, each of the channel segments has length of

L/N μm.

how to spurious overlap capacitances and junction diodes need to be turned off for the sub-devices that are not connected to the drain or source of the composite device, as shown in figure ?

how to nulling the parameters CGS0, CGS1, CGD0, CGD1 and CGB0 will zero the ov erlap capacitance.

erlap capacitance.

L/N μm.

how to spurious overlap capacitances and junction diodes need to be turned off for the sub-devices that are not connected to the drain or source of the composite device, as shown in figure ?

how to nulling the parameters CGS0, CGS1, CGD0, CGD1 and CGB0 will zero the ov

erlap capacitance.

erlap capacitance.