harian

Junior Member level 1

Hi Everybody,

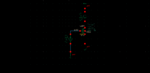

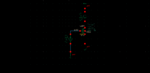

i have a basic Pmos I-v Characteristics question. A PMos in cadence is connected as following(pls, see the below picture)..

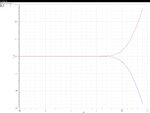

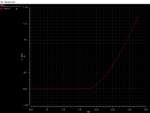

While simulating it, i got pmos diode like curve(pls see belwo)

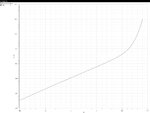

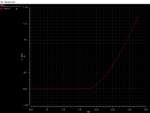

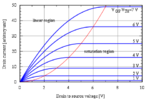

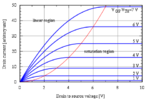

i m excepting a normal pmos I-v charistic like this (naturally inverted)

.

.

can some one explaint he difference. I am simulation with cadence virtuoso.

i have a basic Pmos I-v Characteristics question. A PMos in cadence is connected as following(pls, see the below picture)..

While simulating it, i got pmos diode like curve(pls see belwo)

i m excepting a normal pmos I-v charistic like this (naturally inverted)

.

.can some one explaint he difference. I am simulation with cadence virtuoso.