Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

You could synchronize the two rising edges at one point in time, but not all all the edges obviously, since the two signals are at different frequencies.

So what, exactly, do you want?

So how are these two signals being generated?

Unless the signals are derived from the same master clock, they'll also show a frequency difference, respectively varying phase difference.

It's not clear yet which information is carried by the signals. "Rising edge" (post #1) suggests digital signals, "add them together with summing amplifier" makes only sense for analog signals. In the latter case, digital synchronization methods as previously discussed aren't applicable.

This is a classic recipe for metastability. DON'T DO IT!Sorry about the double post above.

Here's another possible approach:

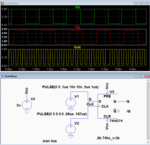

Use a D Flip-Flop with the 1MHz clock going to the D input and the 6MHz clock going to the CLK input.

The FF Q output is then the 1MHz clock with its rising (and falling) edge synchronized to the 6MHz rising edge (differing only by the FF clock to output delay).

This assumes a positive clock edge triggered FF such as the HC4013 or HC74.

LTspice simulation below:

View attachment 138314

If this is a critical circuit than that could be a concern.This is a classic recipe for metastability. DON'T DO IT!