msdarvishi

Full Member level 4

Dear all,

I am coming back to this issue to say the great part of problem issued in the post here got solve but, a new restriction exists that I do not know is it a restriction in Tcl scripting or it can be solved.

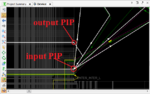

If you look at my attached snapshot, there are 2 PIPs highlighted with red circles that the first in bottom is an input PIP and the one at top is an output PIP. Using Tcl scripting, fortunately I could connect other parasitic wires to the input PIP at bottom as shown with white wires in the picture. You see, all the wires connected to this PIP are exiting this PIP.

The problem is when I am trying to connect a parasitic wire to the PIP at top (please see the second attached snapshot) where the parasitic wires are entering that PIP since the PIP is an output. When I try to connect any of them to that PIP at top, I receive the following error which means the resource of that wires is unknown and it is correct since it does not recognize where that wire comes from !!

.

Can anyone help me how to solve this problem ?

Thanks and Regards,

I am coming back to this issue to say the great part of problem issued in the post here got solve but, a new restriction exists that I do not know is it a restriction in Tcl scripting or it can be solved.

If you look at my attached snapshot, there are 2 PIPs highlighted with red circles that the first in bottom is an input PIP and the one at top is an output PIP. Using Tcl scripting, fortunately I could connect other parasitic wires to the input PIP at bottom as shown with white wires in the picture. You see, all the wires connected to this PIP are exiting this PIP.

The problem is when I am trying to connect a parasitic wire to the PIP at top (please see the second attached snapshot) where the parasitic wires are entering that PIP since the PIP is an output. When I try to connect any of them to that PIP at top, I receive the following error which means the resource of that wires is unknown and it is correct since it does not recognize where that wire comes from !!

Code:

set_property route { { CLBLL_LL_AMUX CLBLL_LOGIC_OUTS_L2 IMUX-L4 SE2END2 } } [get_nets {Inst_StartPoint_DFF/Qs}]

Code:

[COLOR="#FF0000"]ERROR: [Designutils 20-941] Did not find node resource, CLBLL_LOGIC_OUTS_L2, downhill from node, CLBLL_L_X2Y51/CLBLL_LL_AMUX.

Downhill node choices include: CLBLL_L_X2Y51/CLBLL_LOGIC_OUTS20 [/COLOR]Can anyone help me how to solve this problem ?

Thanks and Regards,