Kynix

Banned

Good afternoon~:-DI'm coming again! Thank you for taking time to read my thread.Today I'm also confusing about the FPGA. I hope someone in the forum can help me.:???:

I would like to ask the question about the reading of ARAM.

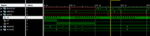

Please look at the following picture,when addr is 2, the dout should be 3.Why it appeared 1 here?

Your help will be appreciated!

Wishes~

I would like to ask the question about the reading of ARAM.

Please look at the following picture,when addr is 2, the dout should be 3.Why it appeared 1 here?

Your help will be appreciated!

Wishes~