leonardwu

Newbie level 5

As we know, when using constant voltage to charge the RC circuit. We can get the following result.

Changing the resistance will change the time constant influencing the rising time and falling time.

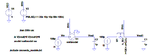

Another situation is to use constant current to charge the capacitor. Here is my issue.

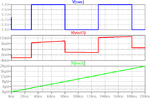

Constant current uses a switch to control charging the capacitor. For the ideal switch, no matter when it turns off/on, the voltage is kept increasing. This is because when switch on, the current goes through a small resistor and charge the capacitor. When switch off, the current goes through a huge resistor but still charge the capacitor with a small current.

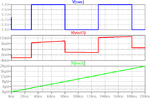

However, when using NMOS transistor as the switch, the voltage behaves as a step signal. When the clock signal goes high, the voltage of the capacitor steps high immediately. When the clock signal stays high, the voltage is increasing linearly. When the clock signal goes to GND, the voltage also steps down a lot.

Does anybody know how to explain this simulation?

Thank you very much.

leonard

Changing the resistance will change the time constant influencing the rising time and falling time.

Another situation is to use constant current to charge the capacitor. Here is my issue.

Constant current uses a switch to control charging the capacitor. For the ideal switch, no matter when it turns off/on, the voltage is kept increasing. This is because when switch on, the current goes through a small resistor and charge the capacitor. When switch off, the current goes through a huge resistor but still charge the capacitor with a small current.

However, when using NMOS transistor as the switch, the voltage behaves as a step signal. When the clock signal goes high, the voltage of the capacitor steps high immediately. When the clock signal stays high, the voltage is increasing linearly. When the clock signal goes to GND, the voltage also steps down a lot.

Does anybody know how to explain this simulation?

Thank you very much.

leonard

Last edited: