farhan89

Junior Member level 3

Hello,

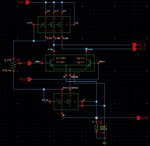

I am simulating differential pair with current mirror and current source (attached image , top is with current source and bottom with current mirror configuration) and I have confusion regarding operating point. I am following Electronics circuits book by tietze and schenk and there it is described that these configurations cannot be used direct for calculating differential and common mode gain with open ended output. For proper operating point a large inductor i.e. 10^9 should be connected at output with a voltage source. I am confused what changes will this bring to the circuit simulation.

Any suggestions or hints for solution ?

Thanks

I am simulating differential pair with current mirror and current source (attached image , top is with current source and bottom with current mirror configuration) and I have confusion regarding operating point. I am following Electronics circuits book by tietze and schenk and there it is described that these configurations cannot be used direct for calculating differential and common mode gain with open ended output. For proper operating point a large inductor i.e. 10^9 should be connected at output with a voltage source. I am confused what changes will this bring to the circuit simulation.

Any suggestions or hints for solution ?

Thanks