Anupama shetter

Newbie level 1

Hello All,

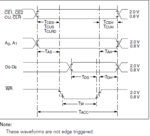

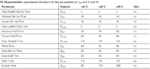

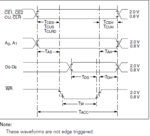

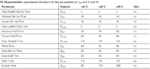

I am engineering student i want write a code in vhdl go get the simulations as per the picture attached and tried doing that but not getting please help me with the code.

thankyou,

I am engineering student i want write a code in vhdl go get the simulations as per the picture attached and tried doing that but not getting please help me with the code.

thankyou,

Code VHDL - [expand]

Last edited by a moderator: