T3STY

Full Member level 4

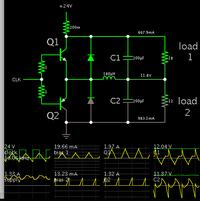

I have just tried the push-pull configurations suggested a few posts behind. It seems they work fine, even though the BJTs heat up a lot, I will need to use good heatsink.

I had no luck testing the circuit posted by BradTheRad though, but I guess it has something to do with the 555 clock, I'll bugfix it later.

I had no luck testing the circuit posted by BradTheRad though, but I guess it has something to do with the 555 clock, I'll bugfix it later.