poorren

Junior Member level 3

Hello,

I'm building a frequency synthesiser using a national semi's PLL. Because, the VCO's tuning voltage is out of the range of PLL power supply. I choose to use a type A active filter as attachment.

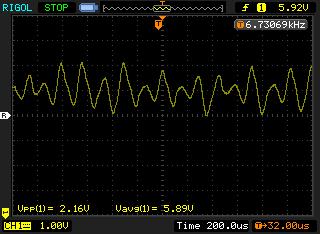

I used National semi's easyPLL to get a loop filter with 3order, and test it in real circuit. I found the voltage of CP (directly connected to OP AMP -) is almost 3.3V, the power supply of PLL, the voltage bias on OP AMP + input has been set to 1.9V. Using Osc Scope, I capture the voltage waveform of CP output, the voltage has short pulse constantly. The pulse has a min voltage 2.8V, max voltage 3.3V. So, I am very confused that what kind of things determinate the voltage of CP? How the current output of CP change to tuning voltage at VCO?

Thanks for your replies and time.

I'm building a frequency synthesiser using a national semi's PLL. Because, the VCO's tuning voltage is out of the range of PLL power supply. I choose to use a type A active filter as attachment.

I used National semi's easyPLL to get a loop filter with 3order, and test it in real circuit. I found the voltage of CP (directly connected to OP AMP -) is almost 3.3V, the power supply of PLL, the voltage bias on OP AMP + input has been set to 1.9V. Using Osc Scope, I capture the voltage waveform of CP output, the voltage has short pulse constantly. The pulse has a min voltage 2.8V, max voltage 3.3V. So, I am very confused that what kind of things determinate the voltage of CP? How the current output of CP change to tuning voltage at VCO?

Thanks for your replies and time.