omara007

Advanced Member level 4

- Joined

- Jan 6, 2003

- Messages

- 1,237

- Helped

- 50

- Reputation

- 102

- Reaction score

- 16

- Trophy points

- 1,318

- Location

- Cairo/Egypt

- Activity points

- 9,716

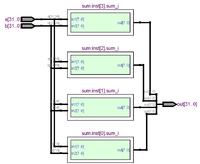

verilog module instantiation

Hi folks

How can I make a conditional instantiation of a certain module in Verilog. In other words, if I have a parameter like (number_of_ports) sit to a specific value .. say '32' .. and I want to instantiate a certain module 32 times accordingly .. I need something to check for the value of this variable and generate the required instances accordingly .. and if I change the value of this variable, the number of instantiated modules will change as a result ..

In VHDL, this is simply implemented as (generate) statement .. if gives you the option to instantiate a generic instance inside the generate loop .. and you easily pass the desired number of instances as the loop counter ..

How can this be implemented in Verilog ?

Hi folks

How can I make a conditional instantiation of a certain module in Verilog. In other words, if I have a parameter like (number_of_ports) sit to a specific value .. say '32' .. and I want to instantiate a certain module 32 times accordingly .. I need something to check for the value of this variable and generate the required instances accordingly .. and if I change the value of this variable, the number of instantiated modules will change as a result ..

In VHDL, this is simply implemented as (generate) statement .. if gives you the option to instantiate a generic instance inside the generate loop .. and you easily pass the desired number of instances as the loop counter ..

How can this be implemented in Verilog ?