swapnil_vlsi

Full Member level 1

verilog integer range

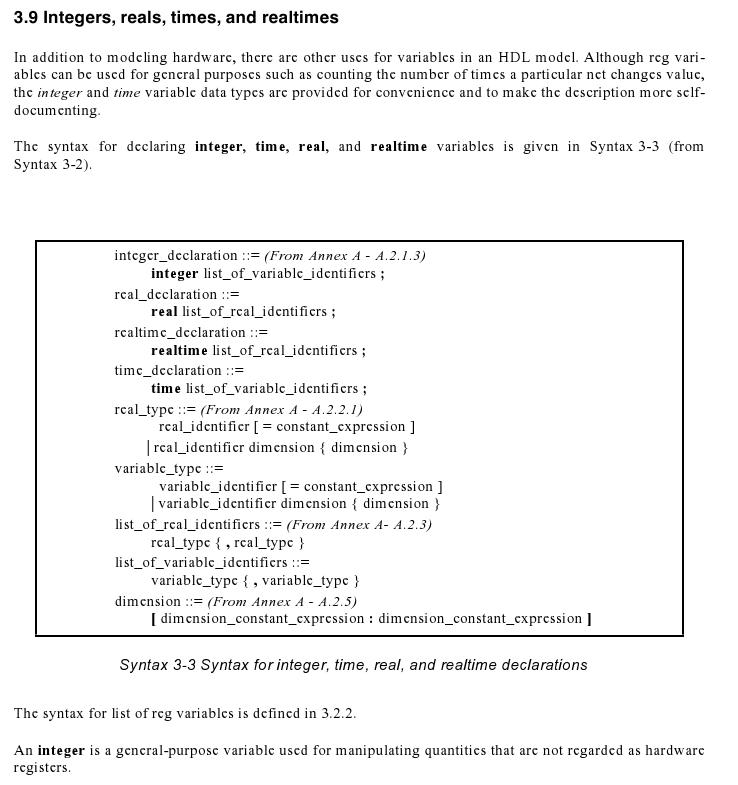

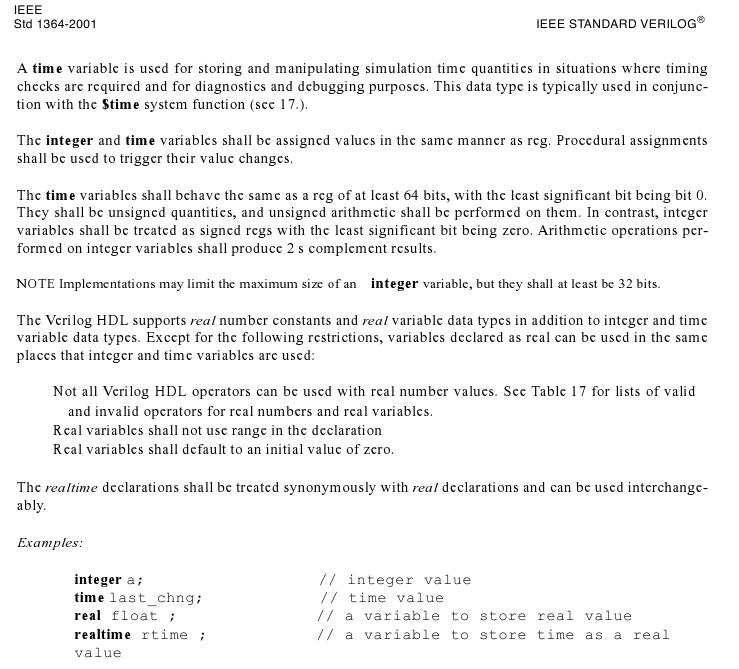

I have a question regarding verilog integer data types. The default

integer size is 32 bit in Verilog. Can we extend it? In VHDL we can

have something like,

Max_Time : in integer range 0 to 255;

How do we express this in Verilog?

Thanks

Swapnil

I have a question regarding verilog integer data types. The default

integer size is 32 bit in Verilog. Can we extend it? In VHDL we can

have something like,

Max_Time : in integer range 0 to 255;

How do we express this in Verilog?

Thanks

Swapnil