xtcx

Advanced Member level 1

- Joined

- Dec 22, 2007

- Messages

- 493

- Helped

- 65

- Reputation

- 130

- Reaction score

- 58

- Trophy points

- 1,308

- Location

- Bangalore, India

- Activity points

- 5,003

hi friends!, I have an issue where my codec sends and receives data at 2MHZ sclk(codec internal) clk.It acts as master and hence the sclk@2MHz isn't controllable by external means. I'll explain in steps.

1) I read\write codec @2MHz sclk(codec clk,master) at the same time on sdi&sdo

2) codec writes 32-bit data to Tx_buffer and reads 32-bits data to Rx_buffer(in FPGA)

3) After reading 32-bits(1 frame) in 16us,the codec goes to idle till 64us.

4) This idle time is to match the sampling time which is 16KHz(64us).

5) The codec reads\writes data @2MHz only or it won't work

6) READ: At 17us,after codec stops writing\reading,I start reading from Tx_buffer (parallel to serial) @1Mbps using FPGA clk @1MHz. So finally I complete my operation at 48us.Remaining 16us is free

7) WRITE: At 17us,after codec stops writing\reading,I start writing to RX_buffer (serial to parallel)@1Mbps using FPGA clk@1MHZ. Again I finish it within 48us.

8 ) BOTH 1MHz read\write to Tx_buffer and Rx_buffer happens from 17us to 48us(32-bits @ 1MHz).

9) This routine is forever.

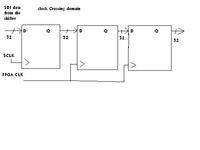

The issue here is that since the codec's clock 2MHz is not accurate when compared to FPGA clk,the FPGA clock shifts faster than codec clk. As a result I find my data missing somewhere...If I simply replace the FPGA 1MHz by codec's (2MHz\2 = 1MHz) 1MHz clk,then I'm able to get my correct audio output...What couldbe the exact reason?....Is this the problem of asynchronous operation?....Isn't the clocks synczing properly?....If every operation is being done using codec Sclk,then I find no problems.

Does anybody have faced this issue? or have any idea related to this?...Does using FIFO could solve this?.....Thanks

1) I read\write codec @2MHz sclk(codec clk,master) at the same time on sdi&sdo

2) codec writes 32-bit data to Tx_buffer and reads 32-bits data to Rx_buffer(in FPGA)

3) After reading 32-bits(1 frame) in 16us,the codec goes to idle till 64us.

4) This idle time is to match the sampling time which is 16KHz(64us).

5) The codec reads\writes data @2MHz only or it won't work

6) READ: At 17us,after codec stops writing\reading,I start reading from Tx_buffer (parallel to serial) @1Mbps using FPGA clk @1MHz. So finally I complete my operation at 48us.Remaining 16us is free

7) WRITE: At 17us,after codec stops writing\reading,I start writing to RX_buffer (serial to parallel)@1Mbps using FPGA clk@1MHZ. Again I finish it within 48us.

8 ) BOTH 1MHz read\write to Tx_buffer and Rx_buffer happens from 17us to 48us(32-bits @ 1MHz).

9) This routine is forever.

The issue here is that since the codec's clock 2MHz is not accurate when compared to FPGA clk,the FPGA clock shifts faster than codec clk. As a result I find my data missing somewhere...If I simply replace the FPGA 1MHz by codec's (2MHz\2 = 1MHz) 1MHz clk,then I'm able to get my correct audio output...What couldbe the exact reason?....Is this the problem of asynchronous operation?....Isn't the clocks synczing properly?....If every operation is being done using codec Sclk,then I find no problems.

Does anybody have faced this issue? or have any idea related to this?...Does using FIFO could solve this?.....Thanks