salem_eng1

Member level 2

Hi All

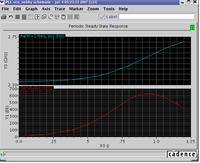

After I design my PLL with VCO gain Kvco=333.MHz/volts and design my system on that after I draw changing of Kvco with input voltage I found it change from Kvco(min)=60 MHz/volt to Kvco(max)=600 MHz/volts with non-Linear curve as shown in the figure.

1- Is this curve is OK or it is a bad design

2- How I can deal with the swep of Kvco on system design and its effect on stability, Lock time, Phase noise ,..........

Note:

Freq Vs Vcontrol in blue

Kvco Vs Vcontrol in red

Thanx

regards

Salem

After I design my PLL with VCO gain Kvco=333.MHz/volts and design my system on that after I draw changing of Kvco with input voltage I found it change from Kvco(min)=60 MHz/volt to Kvco(max)=600 MHz/volts with non-Linear curve as shown in the figure.

1- Is this curve is OK or it is a bad design

2- How I can deal with the swep of Kvco on system design and its effect on stability, Lock time, Phase noise ,..........

Note:

Freq Vs Vcontrol in blue

Kvco Vs Vcontrol in red

Thanx

regards

Salem