ultrasonic

Member level 1

Hello,

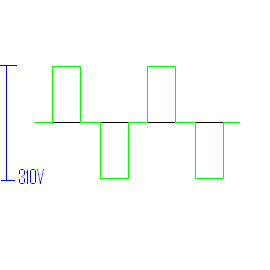

I have tried to boost my low-voltage (12V) PWM signal up to 600Vpp signal. Actually I couldnt get enough help from anywhere, anybody...

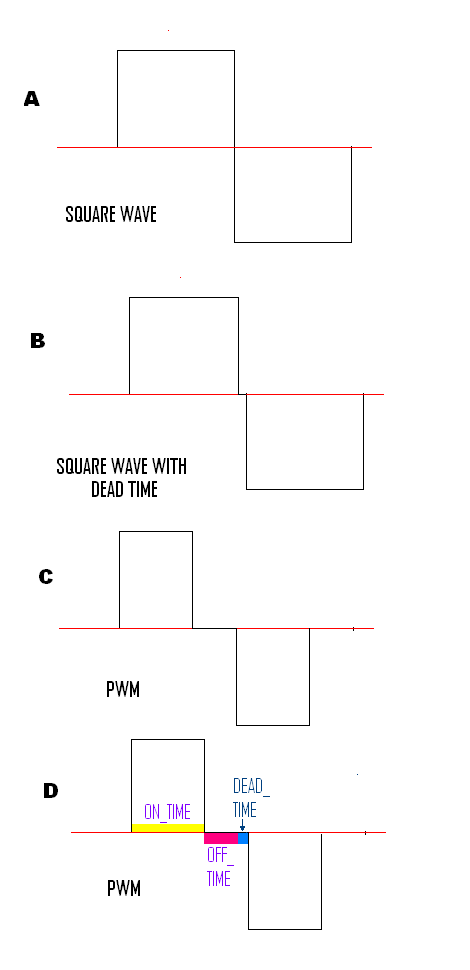

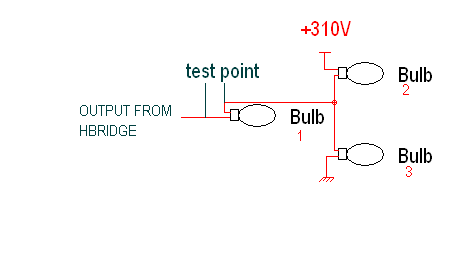

Anyway I have designed and Half bridge with driving Mosfets via IR2110. I read several papers with this usage... I want to ask that which is using to change duty cycle of the output signal? does it change by increasing/decreasing of dead-time or duty cycle? I am using a microcontroller and it generates two PWM signal which if HI is low, LI is high.

Thanks,

I have tried to boost my low-voltage (12V) PWM signal up to 600Vpp signal. Actually I couldnt get enough help from anywhere, anybody...

Anyway I have designed and Half bridge with driving Mosfets via IR2110. I read several papers with this usage... I want to ask that which is using to change duty cycle of the output signal? does it change by increasing/decreasing of dead-time or duty cycle? I am using a microcontroller and it generates two PWM signal which if HI is low, LI is high.

Thanks,