bpramee

Newbie level 4

hi..

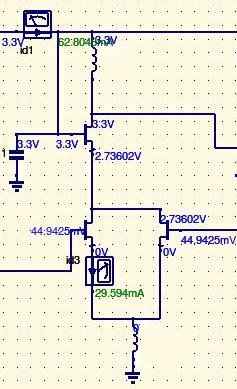

i am trying to design a mesfet low noise amplifier in S band using cascode configuration with Vdd=3.3V . Threshold voltage of mesfet is -0.73. .After calculating the dc bias i got Vgs of upper fet ,M1 (common gate)as 0.57V and that of lower fet,M2 (common source) as 0.04V.

That is M1 is operating in triode region since Vds<Vgs-Vth (3.3<3.3+0.73) and M2 is in saturation.

Is it necessary that M1 also should operate in saturation??current through M2 is 29 mA.Is that current too high??If i try to make M1 in saturation stability will be lost and noisefigure is going beyond limit.. please help

i am trying to design a mesfet low noise amplifier in S band using cascode configuration with Vdd=3.3V . Threshold voltage of mesfet is -0.73. .After calculating the dc bias i got Vgs of upper fet ,M1 (common gate)as 0.57V and that of lower fet,M2 (common source) as 0.04V.

That is M1 is operating in triode region since Vds<Vgs-Vth (3.3<3.3+0.73) and M2 is in saturation.

Is it necessary that M1 also should operate in saturation??current through M2 is 29 mA.Is that current too high??If i try to make M1 in saturation stability will be lost and noisefigure is going beyond limit.. please help