Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

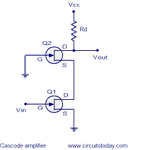

The pic is not a cascode amplifier, it's one of a minimal comparator

(or an op amp, if you added frequency compensation and didn't

care about a lot of things).

The whole point of cascode is, your "steering" device which

has the transconductance-gain, is held at constant(-ish)

voltage so Miller effect (Cgd vs Rgg_sum) is negligible, and

the "guard" device takes the drain voltage swing but returns

the Cgd current to a stiff and not-in-the-gain-lineup point

where it doesn't steal or fight the signal.

But that structure is not illustrated here.

yes, this is 2 stage op amp. thanks for pointing out.

how does the op- amp works.

my understanding is the VINN(-ve) on the btm left nmos will always turn off the btm left nmos, and cause the both pmos to turn on.

then VINP(+ve) will turn on the btm right nmos and cause the voltage current flow to the right part of the pmos.

correct me if i'm wrong.

so my question now is, does this circuit has any miller compensation in it ?

if yes, how?

so my question now is, does this circuit has any miller compensation in it ?

if yes, how?

If there were Miller compensation it would appear as a

capacitor (or possibly drawn as a FET if using that type

of device as a capacitor) attached across the drain and

gate of the output PMOS. But obviously there is not.

The DG cap does not mitigate the miller effect, it utilizes it.

The purpose of miller compensation is pole splitting, creating a dominant low frequency pole and shifting the other pole to higher frequencies.

Hi guys,

how does the cascode amplifier in the pic below helps to solve the miller effect and improve the overall stability.

been reading about the miller effect, still don't quite understand it.

anyone can explained in the most simplest way?

View attachment 130735

This is a "cascade" (not cascode) of a diff amp and a CS amp; or a 2-stage opamp - and here we utilize (rather than "mitigate") Miller effect to improve the phase margin for making the amplifier stable when used in a negative f/b configuration.

.

thanks.

can i said that in cascode configuration, they are designed in that way to mitigate the miller effect.

whereas, in 2 stage op amp with negative feed back configuration, they utilize this miller effect to achieve a stable output at the op amp.