Eshal

Advanced Member level 1

- Joined

- Aug 29, 2012

- Messages

- 470

- Helped

- 16

- Reputation

- 32

- Reaction score

- 15

- Trophy points

- 1,298

- Location

- Nowhere :)

- Activity points

- 5,149

Hello all.

Here is the website I am using for help as my project.

**broken link removed**

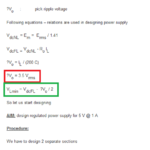

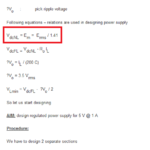

This image is extracted from the above link.

Can you tell me where does the red box formula come? How to derive this formula?

I know 1.41 is the drop of the bridge but this formula doesn't seems to be correct to me. Help me.

Thanks.

Here is the website I am using for help as my project.

**broken link removed**

This image is extracted from the above link.

Can you tell me where does the red box formula come? How to derive this formula?

I know 1.41 is the drop of the bridge but this formula doesn't seems to be correct to me. Help me.

Thanks.