honeybunny

Newbie level 3

There are 4 interview questions about clock frequency. I am very confused about the positive edge and negative edge clock. I mean I understand how they work, but don't quite know how to apply the knowledge I know in the questions, pleae help me solve these three, especially give me some hints about HOW to start with these type of questions. Thank you in advance.

1.

There are 2 DFF in parallel, one clock of those two is positive edge triggered, the other is negative edge triggered. Their outputs go into a NAND2 gate. The output of the NAND2 goes back to the inputs of both DFF. What is the relationship of the NAND2 output's frequency and the clock frequency of the two DFF?

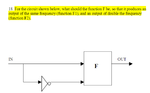

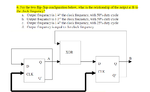

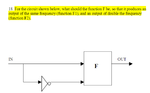

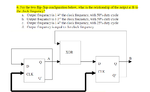

Question 2-4 see the attached pictures.

2.

3.

4.

1.

There are 2 DFF in parallel, one clock of those two is positive edge triggered, the other is negative edge triggered. Their outputs go into a NAND2 gate. The output of the NAND2 goes back to the inputs of both DFF. What is the relationship of the NAND2 output's frequency and the clock frequency of the two DFF?

Question 2-4 see the attached pictures.

2.

3.

4.