muffassir

Member level 3

- Joined

- Sep 15, 2011

- Messages

- 67

- Helped

- 10

- Reputation

- 20

- Reaction score

- 10

- Trophy points

- 1,288

- Location

- Planet Earth

- Activity points

- 1,802

Hi All,

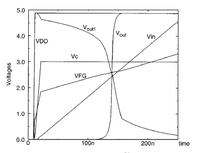

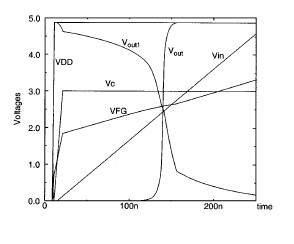

I came across this particular waveform of the Transient analysis see attached image..

DO you all think is it possible to get such waveforms using trans analysis.

What could be the Vin .Is it a square vpulse or traingular vpulse?

Thanks in advance

Muffassir

I came across this particular waveform of the Transient analysis see attached image..

DO you all think is it possible to get such waveforms using trans analysis.

What could be the Vin .Is it a square vpulse or traingular vpulse?

Thanks in advance

Muffassir